为满足对 “纳秒级实时响应” 与 “复杂数据深度运算” 的双重需求,“FPGA+GPU”异构混合部署方案通过硬件功能精准拆分与高速协同,突破单一硬件的性能瓶颈 ——FPGA聚焦低延迟实时交易链路,GPU承接高复杂度数据处理任务,形成 “实时执行+智能分析” 的闭环架构。

1.FPGA+GPU异构架构的优势

高频量化交易的核心矛盾在于 “实时性” 与 “复杂性” 的平衡:

单一FPGA虽能实现纳秒级延迟(端到端≤200ns),但硬件逻辑资源有限(如 Xilinx Alveo U250的LUT资源约35万),难以承载多维度订单流分析、机器学习模型推理等复杂计算(如100个品种的协整检验、LSTM价格预测);

单一GPU虽具备每秒千万级并行运算能力(如NVIDIA A100的FP32算力达19.5TFLOPS),但存在显存通信延迟(约0.5-2μs)与指令调度开销,无法满足做市商、闪电套利等策略对 “微秒必争” 的响应要求;

因此,FPGA+GPU异构架构通过功能互补解决上述矛盾:FPGA承接 “行情→指令→报单” 的低延迟链路,GPU负责“数据→分析→预测”的复杂运算,两者通过高速接口协同,兼顾快与准。

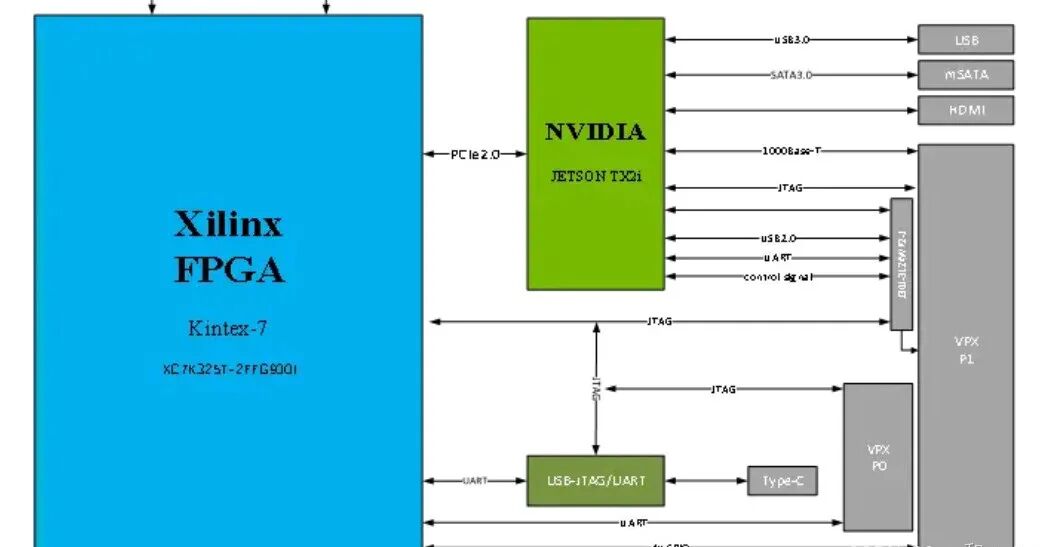

2.FPGA+GPU多层协同核心架构

FPGA+GPU异构方案以功能分层、数据高速流转为核心,整体架构分为三层,各层通过标准化接口衔接,形成无瓶颈的交易闭环:

| 架构层级 | 核心硬件 | 核心功能 | 延迟目标 | 数据流向 |

|---|---|---|---|---|

| 实时执行层 | FPGA(如Xilinx Alveo U250、Intel Stratix 10) | 行情接收解析、交易指令生成、报单发送、风险实时校验 | 端到端≤200ns | 交易所行情→FPGA→GPU(预处理后数据);GPU预测结果→FPGA→交易所报单 |

| 智能分析层 | GPU(如NVIDIA A100、RTX4090) | 订单流深度分析、机器学习模型推理(价格预测、套利机会识别)、多品种风险测算 | 复杂任务≤1ms | FPGA预处理数据→GPU;GPU 分析 / 预测结果→FPGA |

| 数据支撑层 | 高速存储(如NVMe SSD、DDR5)+ 主机CPU | 历史数据缓存、策略参数配置、交易日志存储 | 数据读写≤100ns | 主机→GPU(历史数据);FPGA/GPU→主机(日志 / 结果) |

其中:

1.FPGA与GPU:采用PCIe 4.0/5.0接口(带宽分别达8GB/s、16GB/s,延迟≤10ns),实现纳秒级数据交互;

2.FPGA与交易所:通过100Gbps低延迟光模块(如 Arista 7050X3+DPDK(数据平面开发套件),规避操作系统内核延迟,网络延迟≤1μs;

3.GPU与存储:通过NVMe-oF(NVMe over Fabrics)协议,直接访问远端高速存储,避免CPU中转开销。

3.FPGA与GPU协同

3.1 高速数据交互:PCIe 4.0/5.0的纳秒级传输

硬件接口:采用 PCIe 4.0(带宽8GB/s)或PCIe 5.0(带宽 16GB/s),FPGA 作为PCIe从设备,GPU作为主设备,数据传输延迟≤10ns(远低于高频交易的微秒级需求);

数据格式:统一采用“AXI-Stream流数据格式”(FPGA 侧)与 “CUDA Array格式”(GPU 侧),避免数据格式转换开销;例如,FPGA 将预处理后的订单流数据按 “时间戳+品种ID+价格+成交量” 的固定结构封装,GPU直接按该结构读取,无需解析。

3.2 时间戳同步:PTP协议确保数据一致性

为避免FPGA与GPU的时间戳偏差导致策略误判(如GPU用t=100ns的预测结果,FPGA用 t=200ns的行情执行),通过PTPv2(精确时间协议) 实现时钟同步:

部署PTP主时钟(精度≤1ns),FPGA与GPU均作为从设备,每1ms校准一次时钟,同步误差≤5ns;

所有数据(行情、预测结果、报单)均携带PTP时间戳,FPGA仅执行 “时间戳匹配” 的预测结果(如GPU的t=100ns预测,仅用于FPGAt=100-150ns的行情决策)。

3.3 任务调度:动态优先级分配策略

基于“实时性优先级”动态分配任务:

高优先级任务(如行情解析、报单发送):固定分配给FPGA,独占硬件逻辑资源,确保无延迟波动;

中优先级任务(如订单流特征提取、实时风险测算):FPGA预处理后,GPU并行计算,结果1ms 内反馈;

低优先级任务(如历史回测、参数优化):非交易时段(如盘后)由GPU独占处理,避免占用交易时段资源;

调度实现:通过主机CPU的 “任务调度器”(如基于Linux的RT_PREEMPT实时内核),实时监控 FPGA与GPU的资源利用率,动态调整任务分配(如交易高峰时,暂停GPU的回测任务,优先保障实时分析)。